свойства на продукта:

| ТИП | ОПИСВАМ |

| категория | Интегрална схема (IC) Вградени - микроконтролери |

| производител | NXP USA Inc. |

| серия | MPC56xx Qorivva |

| Пакет | тава |

| състояние на продукта | в наличност |

| ядрен процесор | e200z0h |

| Спецификация на ядрото | 32-битов едноядрен |

| скорост | 64MHz |

| Свързаност | CANbus, FlexRay, LINbus, SPI, UART/USART |

| Периферни устройства | DMA , POR , PWM , WDT |

| Брой I/O | 108 |

| Капацитет за съхранение на програмата | 512KB(512K x 8) |

| Тип програмна памет | светкавица |

| Капацитет на EEPROM | 64K x 8 |

| Размер на RAM | 40K x 8 |

| Напрежение - Захранване (Vcc/Vdd) | 3V ~ 5.5V |

| конвертор на данни | A/D 30x10b |

| Тип осцилатор | вътрешни |

| Работна температура | -40°C ~ 125°C (TA) |

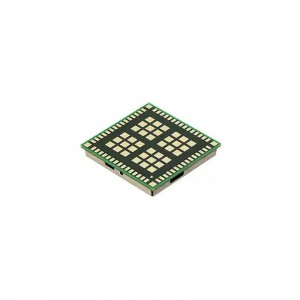

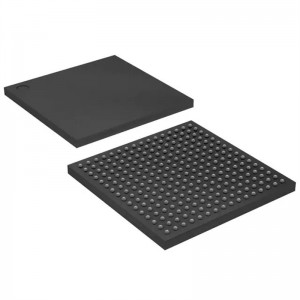

| тип инсталация | Тип повърхностен монтаж |

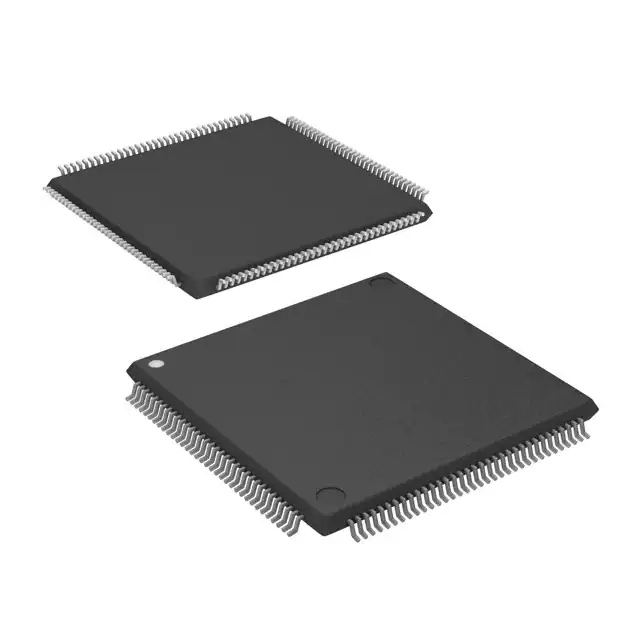

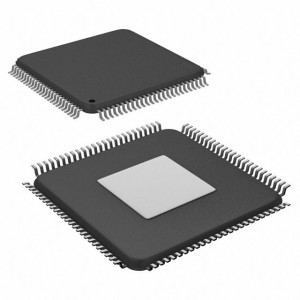

| Опаковка/Приложение | 144-LQFP |

| Опаковка на устройството на доставчика | 144-LQFP(20x20) |

| Основен номер на продукта | SPC5604 |

Околна среда и експортна класификация:

| АТРИБУТИ | ОПИСВАМ |

| RoHS статус | Съвместим със спецификацията ROHS3 |

| Ниво на чувствителност към влага (MSL) | 3 (168 часа) |

| Статус REACH | Продукти извън REACH |

| БЯГСТВО | 3A991A2 |

| HTSUS | 8542.31.0001 |

Резюме на блока от серия MPC5604P:

Блокова функция

Аналогово-цифров преобразувател (ADC) Многоканален, 10-битов аналогово-цифров преобразувател

Модул за подпомагане на стартирането (BAM) Блок от памет само за четене, съдържащ VLE код, който се изпълнява според

режима на зареждане на устройството

Модул за генериране на часовник

(MC_CGM)

Осигурява логика и управление, необходими за генериране на система и периферия

часовници

Мрежа на контролера (FlexCAN) Поддържа стандартния комуникационен протокол CAN

Cross triggering unit (CTU) Позволява синхронизиране на ADC преобразувания със събитие на таймера от eMIOS

или от ДДФЛ

Crossbar превключвател (XBAR) Поддържа едновременни връзки между два главни порта и три подчинени

пристанища;поддържа 32-битова широчина на адресната шина и 32-битова широчина на шината за данни

Cyclic Redundancy Check (CRC) CRC генератор на контролна сума

Deserial сериен периферен интерфейс

(DSPI)

Осигурява синхронен сериен интерфейс за комуникация с външни устройства

Подобрен директен достъп до паметта

(eDMA)

Извършва сложни трансфери на данни с минимална намеса от хост процесор

чрез “n” програмируеми канала

Подобрен таймер (eTimer) Осигурява подобрено програмируемо модулно броене нагоре/надолу

Модул за състояние на коригиране на грешки

(ECSM)

Осигурява безброй различни контролни функции за устройството, включително

видима от програмата информация за нивата на конфигурация и ревизия, нулиране

регистър на състоянието, контрол на събуждането за излизане от режими на заспиване и допълнителни функции

като например информация за грешки в паметта, докладвани от кодове за коригиране на грешки

Външен осцилатор (XOSC) Осигурява изходен часовник, използван като входна референция за FMPLL_0 или като референтна

часовник за конкретни модули в зависимост от нуждите на системата

Блок за събиране на грешки (FCU) Осигурява функционална безопасност на устройството

Флаш памет Осигурява енергонезависимо съхранение за програмен код, константи и променливи

Честотно модулиран

фазово заключена верига (FMPLL)

Генерира високоскоростни системни часовници и поддържа програмируема честота

модулация

Контролер за прекъсване (INTC) Осигурява базирано на приоритет превантивно планиране на заявки за прекъсване

JTAG контролер Осигурява средства за тестване на функционалността и свързаността на чипа, докато остава

прозрачен за системната логика, когато не е в тестов режим

LINFlex контролер Управлява голям брой LIN (Local Interconnect Network protocol) съобщения

ефективно с минимално натоварване на процесора

Модул за въвеждане на режим (MC_ME) Осигурява механизъм за управление на работния режим и режим на устройството

преходни последователности във всички функционални състояния;също управлява блока за управление на мощността,

нулиране на модула за генериране и модула за генериране на часовник и задържа

регистри за конфигурация, управление и състояние, достъпни за приложения

Таймер за периодично прекъсване (PIT) Произвежда периодични прекъсвания и задействания

Периферен мост (PBRIDGE) Интерфейс между системната шина и периферните устройства в чипа

Блок за управление на захранването (MC_PCU) Намалява общата консумация на енергия чрез разединяване на части от устройството

от захранването чрез превключващо устройство за захранване;компонентите на устройството са

групирани в секции, наречени „мощни домейни“, които се контролират от PCU